УДК 621.391, 621.396

ЦИФРОВОЙ ВЫЧИСЛИТЕЛЬНЫЙ СИНТЕЗАТОР СИГНАЛОВ С УГЛОВОЙ МОДУЛЯЦИЕЙ

И. В. Рябов 1, Е. С. Клюжев 2, И. В. Стрельников 3, П. М. Юрьев 2

1 Поволжский Государственный Технологический Университет

2 АО «Марийский Машиностроительный завод»

3 Компания «Новатор»

Статья поступила в редакцию 7 июня 2016 г.

Аннотация. Приведены принципы построения и структурно-схемотехнические решения цифровых вычислительных синтезаторов, построенных на базе метода прямого цифрового синтеза частот и сигналов. Представлены структурная и принципиальная схемы цифрового вычислительного синтезатора частотно-модулированных сигналов, позволяющего синтезировать сигналы с амплитудной, частотной и фазовой модуляцией в диапазоне частот от 0.001 до 200 МГц.

Ключевые слова: прямой цифровой синтез, цифровые вычислительные синтезаторы, ЦАП, функциональный преобразователь код-синус, накопитель частоты, накопитель фазы, уровень амплитудных шумов, фазовый шум.

Abstract. The paper presents principles of construction and structural-circuit design solutions of synthesizer with angle modulation that are based on the direct method of digital synthesis. The research is focused on the methods of formation of complex wideband signals, as well as structure of DDS frequency synthesizer. Synthesizers with angle modulation are used in radar, navigation, adaptive communications systems as the oscillator of the transmitter and the receiver heterodyne. In modern conditions the operation of such systems meets a number of issues relating to the high level of phase noise. Presented synthesizer has the following competitive advantages: a wide range of operating frequencies, high "spectral purity" of the synthesized signal, high tune speed, good repeatability when replicating. Structural scheme of the Direct digital synthesizer to synthesize signals with angle modulation in the frequency range up to 2 GHz is presented, which can be used in modern radars. Spectrograms of output signals are given.

Key words: direct digital synthesis, direct digital synthesizers, digital-to-analog converter, function converter code-sine, frequency accumulator, phase accumulator, amplitude noise level, phase noise.

Введение

В настоящее время цифровые вычислительные синтезаторы все больше вытесняют аналоговые синтезаторы с фазовой автоподстройкой частоты, так как они обладают высокими техническими характеристиками [1].

Появление цифровых методов синтеза частот и сигналов позволило значительно улучшить технические характеристики РТС: в радиовещании и телевидении – улучшить качество звуковых и телевизионных сигналов; в радиорелейных и спутниковых системах связи – повысить качество телефонной и телевизионной связи; в радиолокации – повысить разрешающую способность по дальности и по скорости; в навигации – снизить ошибки определения координат объекта; в радиосвязи – улучшить помехоустойчивость, скрытность и надежность сеанса связи [2].

Достоинства цифровых вычислительных синтезаторов: широкий диапазон синтезируемых частот, сверхмалый шаг сетки частот, экстремально быстрая скорость перестройки частоты, непрерывность фазы при перестройке частоты, низкий уровень фазовых шумов, простой алгоритм формирования сложных сигналов, возможность независимого управления амплитудой, фазой и частотой синтезируемого сигнала, хорошая повторяемость параметров при тиражировании, удобство управления при помощи цифрового интерфейса, стабильность параметров при воздействии дестабилизирующих климатических и механических воздействиях. Недостатки ЦВС: значительное влияние джиттер-фактора опорного генератора, сравнительно высокий уровень амплитудных шумов, который зависит от разрядности используемого ЦАП на выходе цифрового синтезатора.

В настоящее время разработаны основные принципы построения цифровых вычислительных синтезаторов (ЦВС), в значительной степени изучены их особенности и характеристики формируемых сигналов. Однако недостаточно исследованы предельные возможности ЦВС по быстродействию и «чистоте спектра» формируемых сигналов. Развитие ЦВС в настоящее время идет в основном в рамках известных структурных схем по пути их интегральной реализации, технологического повышения быстродействия, снижения энергопотребления и стоимости [3].

Цель работы заключается в расширении функциональных возможностей ЦВС, позволяющего синтезировать сигналы с частотной и фазовой модуляцией.

ЦВС, построенный на базе метода прямого цифрового синтеза

Цифровые вычислительные синтезаторы (ЦВС) характеризуются тем, что формируемый ими сигнал синтезируется с высокой точностью. Амплитуда, частота, и фаза сигнала в любой момент времени точно определены, что дает возможность управлять ими при помощи цифрового интерфейса. ЦВС устойчивы к температурному дрейфу. в меньшей степени подвержены старению. Единственным функциональным узлом, который обладает свойственной аналоговым схемам нестабильностью, является ЦАП. Поэтому ЦВС получают все большее распространение.

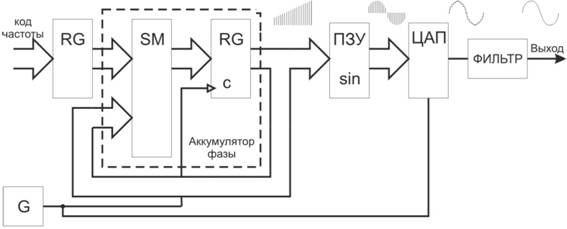

Структурная схема ЦВС на основе накапливающего сумматора представлена на рис.1 [5-7].

Рис. 1. Цифровой вычислительный синтезатор на основе аккумулятора фазы

Опорный генератор G формирует сигнал тактовой частоты, который служит для синхронизации работы узлов ЦВС: цифрового накопителя (аккумулятора фазы) и ЦАП.

На вход регистра памяти поступает код начальной частоты Ci. Содержимое аккумулятора фазы с каждым тактовым импульсом T=Δt линейно увеличивается во времени, и зависит от величины кода Ci. Выходной код аккумулятора фазы представляет собой код мгновенной фазы выходного сигнала. Постоянное приращение представляет собой приращение фазы за один такт работы устройства. Чем больше значение кода Ci, тем быстрее изменяется фаза во времени, и, следовательно, больше частота генерируемого сигнала.

Далее линейно нарастающий код фазы подается на вход функционального преобразователя код-синус, представляющий собой постоянное запоминающее устройство, в котором записаны значения кодов синуса.

Задача ЦВС заключается в получении на выходе сигнала синусоидальной формы с заданной частотой. Так как в ЦВС формирование выходного сигнала происходит в цифровой форме, очевидна необходимость цифроаналогового преобразователя (ЦАП) и фильтра нижних частот (ФНЧ).

Чтобы получить синусоидальный сигнал, на вход ЦАП необходимо подать последовательность отсчетов функции синуса sin(x), следующих с частотой дискретизации. Закон изменения функции sin(x) во времени сложен и цифровыми методами просто не реализуется. Поэтому наиболее подходящим методом формирования отсчетов функции sin является табличный метод, который реализуется посредством ввода в постоянное запоминающее устройство (ПЗУ) таблицы соответствий код х–sin(x), отсчеты с выхода ПЗУ поступают на ЦАП, который формирует на выходе ступенчатый синусоидальный сигнал, подвергающийся фильтрации в ФНЧ и поступающий на выход ЦВС.

Аккумулятор фазы работает с периодическими переполнениями, обеспечивая арифметику по модулю 2N. Такое периодическое переполнение соответствует периодическому поведению функции sin(x) с периодом 2π. Другими словами, частота переполнений аккумулятора фазы равна частоте выходного сигнала. Это частота определяется формулой:

![]() , (1)

, (1)

где ![]() – выходная

частота,

– выходная

частота,

![]() –

тактовая частота,

–

тактовая частота,

Ci – код начальной частоты,

N – разрядность аккумулятора фазы.

Шаг перестройки частоты определяется формулой

![]() , (2)

, (2)

Например, если тактовая частота равна fт = 100 МГц, а разрядность N = 32, то шаг перестройки частоты составит примерно Δf = 0,02 Гц.

Из этого соотношения следует, что если увеличить разрядность N, то уменьшится шаг перестройки частоты. Увеличение разрядности аккумулятора фазы не требует обязательного увеличения разрядности адреса ПЗУ. Для адресации можно использовать лишь необходимое количество старших разрядов кода фазы. Для уменьшения объема ПЗУ можно использовать свойства симметрии функции sin(x). В большинстве ЦВС в ПЗУ содержится только 1/4 периода функции.

Таким образом, в ЦВС аккумулятор фазы формирует последовательность кодов мгновенной фазы сигнала, которая изменяется линейно. Скорость изменения фазы задается кодом частоты. Далее с помощью ПЗУ линейно нарастающий код фазы преобразуется в изменяющиеся по синусоидальному закону отсчеты выходного сигнала. Эти отсчеты поступают на ЦАП, на выходе которого формируется ступенчатый синусоидальный сигнал. Этот ступенчатый синусоидальный сигнал фильтруется с помощью аналогового ФНЧ, на выходе которого получается синусоидальный сигнал [8].

Для того чтобы правильно применять ЦВС, необходимо иметь четкое представление о том, как различные факторы влияют на его выходные характеристики. Важнейшими характеристиками синтезатора являются: нестабильность частоты, дрожание выходного сигнала («джиттер»), уровень амплитудных и фазовых шумов.

Главным

источником фазовых шумов в ЦВС является генератор тактового сигнала. Фазовый

шум выходного сигнала синтезатора теоретически меньше фазового шума сигнала

тактового генератора на ![]() дБ.

дБ.

На практике это улучшение ограничено свойствами схем, входящих в состав синтезатора (типовое значение составляет –130 дБ/Гц при расстройке на 1 кГц от выходной частоты) [1].

Некоторые типы высокочастотных ЦВС содержат встроенный умножитель частоты на основе ФАПЧ. Однако умножение частоты в несколько раз вызывает увеличение фазового шума.

Аккумуляторы фазы серийно выпускаемых ЦВС имеют разрядность 32 или 48 бит. Но только часть старших разрядов используется для адресации ПЗУ, в которое записаны коэффициенты функции sin(x). Это вынужденная мера, связанная с необходимостью уменьшения объема ПЗУ. [2].

Отсечение младших разрядов кода адреса ПЗУ приводит к возникновению ошибки в представлении фазы. Как следствие, это приводит к появлению погрешности при преобразовании фазы в амплитуду выходного сигнала. Эта погрешность является периодической, так как в зависимости от кода частоты одно и то же состояние аккумулятора фазы повторяется чаще или реже. В результате в спектре выходного сигнала синтезатора появляются дискретные составляющие, возникающие из-за усечения кода фазы. Значения амплитуды и фазы этих составляющих зависят от разрядности аккумулятора фазы (N), разрядности слова фазы после усечения (Nус) и значения кода частоты (Ci).

Например, при Nус = 15 максимальный уровень этих составляющих приблизительно равен –90 дБ. Причем наихудшим является случай, когда в отбрасываемой части кода фазы старший бит равен «1», а все остальные биты – «0». Дополнительные составляющие в спектре будут отсутствовать при условии, что в отбрасываемой части кода все составляющие равны нулю.

На рис. 2 приведены зависимости уровня побочных спектральных составляющих от разрядности кода фазы для ЦАП различной разрядности. Неограниченно наращивать разрядность кода фазы нет необходимости потому, что снижение уровня побочных компонентов происходит только до определенного значения, зависящего от уровня шумов квантования ЦАП. На практике разрядность кода фазы должна быть на 2-3 разряда больше, чем разрядность ЦАП.

Рис.2. Зависимость уровня амплитудных шумов ЦВС от разрядности ЦАП

Следует отметить, что существуют методы уменьшения влияния усечения кода фазы, основанные на добавлении к фазовой информации псевдослучайного шума. Таким образом, удается уменьшить энергию соответствующих побочных компонентов, но при этом увеличивается общий шумовой порог [6].

Как уже было сказано, максимальная выходная частота синтезируемого сигнала не может быть выше половины тактовой частоты fт, а на практике она в 4 раза меньше тактовой частоты [1-3].

Огибающая спектра сигнала на выходе ЦАП изменяется по закону sin(x)/x, и амплитуду сигнала можно определить по формуле:

(3)

(3)

где ![]() – амплитуда

сигнала на выходе ЦАП на заданной частоте.

– амплитуда

сигнала на выходе ЦАП на заданной частоте.

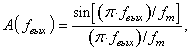

ЦВС - схема электрическая структурная

Цифровой вычислительный синтезатор с угловой модуляцией (рис. 3) содержит первый регистр памяти 1, первый цифровой накопитель (накопитель частоты) 2, второй цифровой накопитель (накопитель фазы) 3, сумматор 4, преобразователь кодов x-sin(x) 5, цифроаналоговый преобразователь (ЦАП) 6, фильтр нижних частот (ФНЧ) 7, второй регистр памяти 8, делитель частоты с переменным коэффициентом деления (ДЧПКД) 9, третий регистр памяти 10, эталонный генератор 11, блок формирования и задержки 12 [10].

Рис.3. Цифровой вычислительный синтезатор сложных широкополосных сигналов. Схема электрическая структурная

Цифровой вычислительный синтезатор работает следующим образом.

Эталонный генератор 11 выдает синусоидальный сигнал опорной частоты, который поступает на вход блока формирования и задержки 12. В блоке формирования и задержки 12 формируются последовательности прямоугольных импульсов, служащие для синхронизации узлов ЦВС: первого цифрового накопителя (накопителя частоты) 2, второго цифрового накопителя (накопителя фазы) 3, цифроаналогового преобразователя (ЦАП) 6, делителя частоты с переменным коэффициентом деления (ДЧПКД) 9.

На вход первого регистра памяти 1 поступает код начальной частоты Ci, одновременно на вход второго регистра памяти 8 поступает код Dk, определяющий коэффициент деления делителя частоты 9, а на вход третьего регистра памяти 10 – код Hi, определяющий начальную фазу синтезируемого сигнала.

С первым тактовым импульсом в момент ![]() код начальной частоты Ci из первого регистра памяти 1 записывается в первый цифровой

накопитель 2; код коэффициента деления Dk из второго регистра памяти 8 записывается в делитель частоты с

переменным коэффициентом деления 9, а код начальной фазы Hi из третьего регистра памяти 10 поступает на второй вход сумматора

4.

код начальной частоты Ci из первого регистра памяти 1 записывается в первый цифровой

накопитель 2; код коэффициента деления Dk из второго регистра памяти 8 записывается в делитель частоты с

переменным коэффициентом деления 9, а код начальной фазы Hi из третьего регистра памяти 10 поступает на второй вход сумматора

4.

Затем с каждым тактовым импульсом на выходе первого цифрового накопителя (накопителя частоты) 2 код А будет изменяться по формуле:

![]() . (4)

. (4)

Код А поступает на вход второго цифрового накопителя (накопителя фазы) 3, результат суммирования в котором будет изменяться по формуле:

![]() . (5)

. (5)

Код В поступает на первый вход сумматора 4, на второй вход сумматора 4 поступает код Hi с выхода третьего регистра памяти 10.

Код суммы S на выходе сумматора 4 изменяется по формуле:

![]() . (6)

. (6)

Результат суммирования S с выхода сумматора 4 поступает на вход преобразователя кодов 5, где

происходит преобразование код S – sin(S). Далее код синуса sin(S) поступает на вход ЦАП 6, на выходе которого формируется

ступенчатый сигнал «синусоидальной» формы, который подается на ФНЧ 7. Фильтр

нижних частот 7 имеет частоту среза ![]() , где

, где ![]() – тактовая частота и пропускают на выход синтезатора только первую

гармонику сформированного сигнала.

– тактовая частота и пропускают на выход синтезатора только первую

гармонику сформированного сигнала.

Если принять, что ![]() – начальная фаза,

– начальная фаза, ![]() – начальная частота;

– начальная частота; ![]() – скорость изменения частоты

синтезируемого сигнала,

– скорость изменения частоты

синтезируемого сигнала, ![]() – период следования

тактовых импульсов, то тогда на выходе ФНЧ 7 формируется сигнал, амплитуда

которого изменяется по формуле:

– период следования

тактовых импульсов, то тогда на выходе ФНЧ 7 формируется сигнал, амплитуда

которого изменяется по формуле:

![]() , (7)

, (7)

где Um – амплитуда сигнала,

![]() – начальная частота

синтезируемого сигнала,

– начальная частота

синтезируемого сигнала,

![]() – скорость изменения частоты синтезируемого сигнала,

– скорость изменения частоты синтезируемого сигнала,

![]() – начальная фаза

синтезируемого сигнала,

– начальная фаза

синтезируемого сигнала,

Таким образом, задавая коды: начальной частоты - Ci, код начальной фазы - Hi, код Dk, определяющий скорость изменения частоты, можно управлять начальной фазой, частотой и скоростью изменения частоты синтезируемого сигнала.

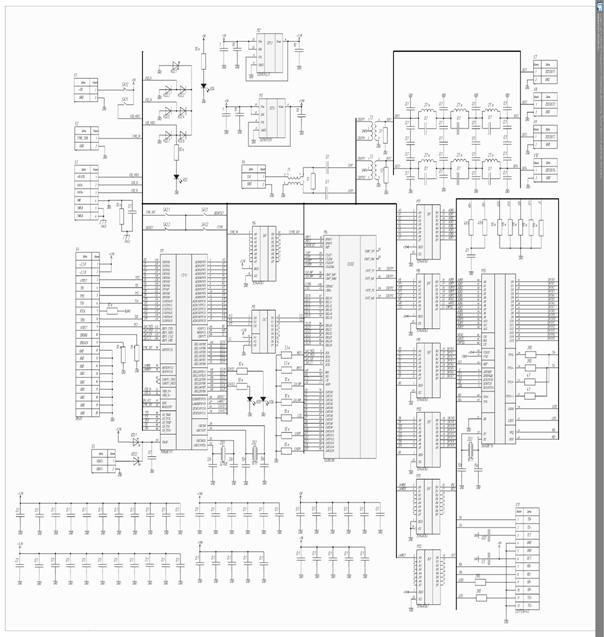

ЦВС - схема электрическая принципиальная

Цифровой вычислительный синтезатор (рис.4) содержит:

Модулятор, предназначенный для преобразования двоичных данных, поступающих на входные порты по протоколу USB 2.0 (разъем X3) или IEE 802.3/Ethernet (разъем X11) с внешнего устройства (персональный компьютер или любое другое внешнее устройство, поддерживающее упомянутые стандарты передачи данных), в модулированные сигналы, формирующиеся на выходах X7, X8, X9, X10.

Напряжение питания схемы 5В, ток потребления до 2А. Схема может питаться через внешний разъем низковольтного питания X1, либо через разъем X3, предназначенный для подключения по USB, которые выбираются переключателем SA1. О наличии напряжения питания сигнализирует светодиод VD4. Поскольку в модуляторе имеются цепи, требующие напряжений питания +1,8В, +3,3В и +5В, то схема питания содержит стабилизатор на +3,3В на основе микросхемы М2 1309ЕН3,3Т, а также стабилизатор на +1,8В на основе микросхемы М3 1309ЕН1,8Т.

Основу ц.в.с. составляет микросхема М1 32-разрядного микроконтроллера 1986ВЕ91Т с ядром ARM Cortex-M3, управляющая микросхемой М6 1508ПЛ8Т – цифрового вычислительного синтезатора.

Ц.в.с. построен по схеме, содержащей шину адреса, шину данных, а также шину управления, которая идет от микроконтроллера М1 к синтезатору М6, а также к контроллеру М13 локальной вычислительной сети уровня звена данных протокола IEE 802.3/Ethernet.

Шина адреса 16-разрядная, шина данных 16-разрядная, шина управления включает себя сигналы чтения RD, записи WR, а также выборки. Выборку кристалла среди микросхем М6 и М13 осуществляет дешифратор М6 в зависимости от выставляемого микроконтроллером М1 адреса на шине адреса.

В задачи микроконтроллера входит инициализация и управление микросхемой М6, инициализация М13, обмен данными по USB и по Ethernet, отсчет реального времени, вывод состояния модулятора на светодиоды индикации VD5, VD6. Для организации резервного питания внутренней схемы, ведущей отсчет реального времени в составе М1, реализовано подключение к разъему-держателю X5 батареи типа CR2032 через схему на диодах Шоттки VD1.1 и VD1.2 на случай отключения внешнего питания. Для отсчета реального времени к микроконтроллеру М1 подключена схема внешнего кварцевого резонатора ZQ1, настроенная на частоту 32768 Гц. Тактирование микроконтроллера М1 внутреннее с внешним подключением кварцевого резонатора ZQ2 на 16 МГц. Разъем X4 предназначен для программирования М1. Микроконтроллер поддерживает обмен данными по протоколу USB 2.0, поэтому разъем X3 для организации передачи по USB 2.0 подсоединен напрямую к микроконтроллеру М1. Предельная скорость передачи порта USB 12 Мбит. Для электростатической защиты входов микроконтроллера М1 к линиям данных шины USB подсоединена диодная сборка VD2. Светодиод VD3 предназначен для индикации внешнего подключения хоста к схеме ц.в.с. по интерфейсу USB 2.0.

Поскольку микросхема М13 работает при напряжении +5В, а микроконтроллер М1 работает при напряжении +3,3В, то для корректного обмена данными между М1 и М13 необходимо согласование напряжений логического нуля и логической единицы по уровню. Для этого в схеме модулятора присутствуют буферы, М7, М8, М9, М10, М11, М12, которые согласуют шину адреса (М7, М8), шину данных (М9, М10), сигналы чтения RD, записи WR, выборки CS2 (М8). Кроме того, для увеличения скорости передачи данных по ЛВС Ethernet на микроконтроллер М1 с микросхемы М13 через согласующий буфер М11 заведены сигналы прерывания LANIRQ, а также готовности LANRDY. Вход перезагрузки М13 соединен с выходом микросхемы М1. Тактирование микросхемы М13 внутреннее с подключением внешнего кварцевого резонатора ZQ2, Предельная скорость передачи порта Ethernet 10 Мбит.

Микросхема М6 представляет собой двухканальный цифровой вычислительный синтезатор. Обеспечивает формирование гармонических квадратурных колебаний и сигналов с линейно-частотной модуляцией (ЛЧМ), амплитудно-фазовой (QAM), частотной и фазовой манипуляцией (ЧМ и ФМ) на частоте дискретизации до 1 ГГц.

Выходные сигналы М6 поступают на разъем X7 без фильтрации для канала 1, на разъем X9 с выхода схемы фильтрации для канала 1, на разъем X8 без фильтрации для канала 2, на разъем X10 с выхода схемы фильтрации для канала 2. Источник частоты дискретизации внешний, подключаемый к М6 через коаксиальный разъем X5. Управление синтезатором М6, а также загрузка кодов частоты и фазы с М1 осуществляется через 16-разрядные шины адреса и данных, либо через SPI. Выбор профилей для синтеза сигналов осуществляется через выделенные шины управления, каждая из которых содержит сигналы SEL10, SEL11, SEL12, SEL13,SEL14,SEL15 для 1 канала и сигналы SEL20, SEL21, SEL22, SEL23,SEL24,SEL25 для 2 канала соответственно. Синхронизация работы модулятора с внешними устройствами осуществляется сигналом, поступающим от внешних устройств на разъем X2.

Схема ц.в.с.. работает следующим образом. При включении питания происходит инициализация микроконтроллера М1, инициализация синтезатора М6, инициализация М13. При инициализации М1 происходит инициализация портов, инициализация USB, инициализация интерфейса SPI для связи c М6. Далее микроконтроллер М1 инициализирует М6, записывая во внутреннюю память стандартные профили, которые хранятся во внутренней EEPROM микроконтроллера М1. Затем микроконтроллер М1 производит настройку М13 на прием и передачу данных по параллельной шине. Схема готова к приему внешних сигналов, среду которых могут быть внешние сигналы по USB, внешние сигналы по Ethernet, внешние сигналы синхронизации. По приходу пакета данных по USB или Ethernet микроконтроллер М1 выделяет из пакета команду и данные, обрабатывает их и выполняет соответствующие действия.

По приходу внешнего сигнала синхронизации с разъема X5 синтезатор осуществляет немедленную генерацию сигналов по заранее запрограммированному сценарию.

Рис.4. Цифровой вычислительный синтезатор сложных широкополосных сигналов. Схема электрическая принципиальная

Основные технические параметры ЦВС:

Тактовая частота: 800 МГц,

Диапазон частот формируемых сигналов: 0,001 – 200 МГц,

Шаг перестройки частоты: 1,5 * 10-6 Гц,

Разрядность накопителя частоты: 48,

Разрядность накопителя фазы: 48,

Разрядность ЦАП: 10,

Амплитуда выходного сигнала: 300 мВ,

Виды модуляции сигналов: амплитудная (АМ), частотная (FSK),

фазовая (PSK),

Уровень амплитудных шумов: менее – 60 дБ/В,

Напряжение питания периферии 3,3 В.

Напряжение питания ядра 1,8 В.

Цифровой вычислительный синтезатор 1508ПЛ8Т имеет два канала синтеза выходных сигналов, поэтому, задавая коды начальной фазы в первом и втором канале, отличающиеся на 900, можно сформировать квадратурные частотно-модулированные сигналы, которые можно описать формулой (7). Далее они через согласующие трансформаторы поступают на ФНЧ, имеющие частоту среза 300 МГц, где происходит выделение только первой гармоники синтезируемых сигналов и подавление гармоник высших порядков. Данный ЦВС обладает широкими функциональными возможностями, позволяет синтезировать сигналы с амплитудной, частотной и фазовой модуляцией; управление ЦВС осуществляется программой, предварительно записанной в микроконтроллер М2.

Заключение

Сравнительный анализ современных методов синтеза частот и сигналов показал, что наиболее перспективным для радиотехнических и телекоммуникационных систем, является метод прямого цифрового синтеза, который обладает следующими преимуществами: высокой технологичностью и надежностью, малым шагом по частоте, высокой скоростью перестройки частоты при непрерывности фазы формируемых колебаний, способностью формирования сложных сигналов, хорошей повторяемостью параметров при тиражировании.

Предложенный цифровой вычислительный синтезатор сложных широкополосных сигналов позволяет синтезировать сигналы с частотной, фазовой и амплитудной модуляцией, причем управление цифровым вычислительным синтезатором осуществляется при помощи удобного цифрового интерфейса.

Данный ЦВС может быть использован в качестве возбудителя передатчиков и гетеродинов приемников современных адаптивных систем КВ и УКВ связи с псевдослучайной перестройкой рабочей частоты, что позволит увеличить помехоустойчивость и надежность сеанса связи, а также в аппаратно-программном радиокомплексе для дистанционного зондирования ионосферы Земли для получения амплитудно-частотных и дистанционно-частотных характеристик радиолиний.

Литература

1. Ямпурин Н. П. Формирование прецизионных частот и сигналов: Учеб. пособие / Н. П. Ямпурин, В. В. Болознев, Е. В. Сафронов, Е. Б. Жалнин. – Нижний Новгород: Нижегородский государственный технический университет, 2003. – 187 с.

2. Белов Л.А. Формирование стабильных частот и сигналов. М.: ИЦ «АКАДЕМИЯ», 2005.

3. Рябов И. В. Цифровой синтез прецизионных сигналов: Монография / И. В. Рябов. – Йошкар-Ола: Марийский государственный технический университет, 2005. – 152 с.

4. Рябов И.В. Цифровые синтезаторы частотно-модулированных сигналов // Приборы и техника эксперимента, 2001. № 2. С.62-69.

5. Рябов И.В. Цифровой синтезатор с V-образным законом изменения частоты // Приборы и техника эксперимента, 2006, № 3. С. 88-90.

6. Ryabov I.V. Digital Synthesizers of Frequency-Modulated Signals // Instruments and Experimental Techniques. V. 44. № 2. 2001. P.62-68.

7. Ryabov I.V. Digital Calculating Synthesizer with V-shaped Law Of Frequency Change // Instruments and Experimental Techniques. V. 49. №3. 2006. P.376-378.

8. Рябов И.В. Метод прямого цифрового синтеза прецизионных сигналов // Радиотехника, 2006. № 9. С.14-17.

9. Патент № 2058659 Российской Федерации МКИ Н03В 19/00. Цифровой синтезатор частот / Рябов И.В., Фищенко П.А. Заявл. 23.09.93. Опубл. 20.04.1996. Бюл.№ 11. 4 с.

10. Патент № 2490789 Российской Федерации МПК Н03L 7/18. Цифровой синтезатор фазомодулированных сигналов / Рябов И.В., Дедов А.Н., Толмачев С.В. Заявл. 18.07.2012. Опубл. 20.08.2013. Бюл.№ 23. 7 с.

11. Vankka, J. Direct digital synthesizers Theory and Application// Proc. Int. Symp. Circuits and Systems ISCAS’03. – 2006. – 210 p.

12. Wang, C.-C. Phase-Adjustable Pipelining ROM-Less Direct Digital Frequency Synthesizer With a 41.66-MHz Output Frequency / C.-C. Wang, J.-M. Huang, Y.-L. Tseng // Circuits and Systems II: Express Briefs, IEEE Transactions. – 2006. – V.53. – P.1143-1147.